-

個(gè)人品牌修煉ABC-浙江銘生

-

方旭:一個(gè)律師的理想信念-浙江銘生

-

筆記:如何追加轉(zhuǎn)讓股權(quán)的未出資股東為被執(zhí)行人

-

生命中無(wú)法缺失的父愛(ài)(婚姻家庭)

-

律師提示:如何應(yīng)對(duì)婚前財(cái)產(chǎn)約定

-

搞垮一個(gè)事務(wù)所的辦法有很多,辦好一個(gè)事務(wù)所的方法卻只有一個(gè)

-

顛覆認(rèn)知:語(yǔ)文數(shù)學(xué)總共考了96分的人生會(huì)怎樣?

-

寧波律師陳春香:爆款作品創(chuàng)作者如何提醒網(wǎng)絡(luò)言論的邊界意識(shí)

-

搖號(hào)成功選房后還可以后悔要求退還意向金嗎

-

誤以為“低成本、高回報(bào)”的假離婚,多少人誤入歧途

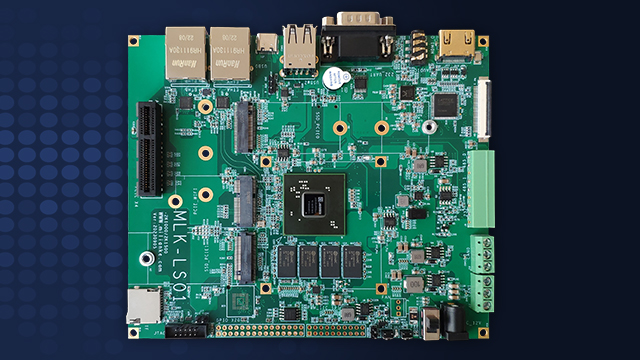

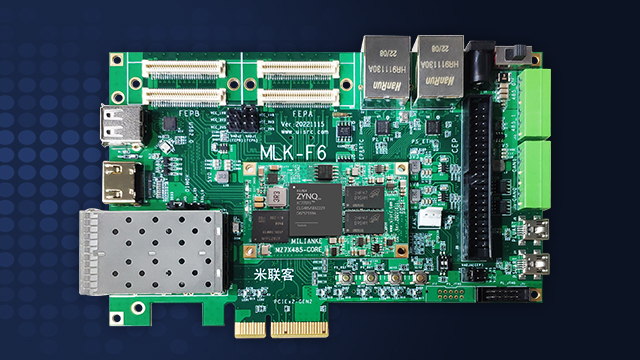

江西安路FPGA開(kāi)發(fā)板芯片

FPGA 開(kāi)發(fā)板的升級(jí)與拓展能力為其應(yīng)用帶來(lái)更多可能性。隨著技術(shù)發(fā)展,開(kāi)發(fā)者可通過(guò)更新 FPGA 的配置文件,為開(kāi)發(fā)板添加新功能或優(yōu)化現(xiàn)有功能。許多開(kāi)發(fā)板預(yù)留拓展接口,開(kāi)發(fā)者可根據(jù)項(xiàng)目需求添加額外功能模塊。如在圖像識(shí)別項(xiàng)目中,添加攝像頭模塊獲取圖像數(shù)據(jù);在定位導(dǎo)航項(xiàng)目中,接入 GPS 模塊獲取位置信息。這種升級(jí)與拓展能力使 FPGA 開(kāi)發(fā)板能夠適應(yīng)不斷變化的應(yīng)用需求,延長(zhǎng)開(kāi)發(fā)板的使用壽命,提高其性價(jià)比,在不同項(xiàng)目與應(yīng)用場(chǎng)景中持續(xù)發(fā)揮重要作用,滿足開(kāi)發(fā)者多樣化的開(kāi)發(fā)需求。FPGA 開(kāi)發(fā)板的低功耗設(shè)計(jì),適用于便攜式設(shè)備與電池供電場(chǎng)景。江西安路FPGA開(kāi)發(fā)板芯片

FPGA開(kāi)發(fā)板在金融領(lǐng)域的應(yīng)用逐漸興起,為金融科技的發(fā)展帶來(lái)新的機(jī)遇。在高頻交易系統(tǒng)中,時(shí)間就是金錢,對(duì)數(shù)據(jù)處理速度和實(shí)時(shí)性要求極高。FPGA開(kāi)發(fā)板憑借其高速并行處理能力,能夠獲取金融市場(chǎng)的實(shí)時(shí)行情數(shù)據(jù)。通過(guò)預(yù)先編寫的交易算法,開(kāi)發(fā)板對(duì)這些數(shù)據(jù)進(jìn)行實(shí)時(shí)分析和處理,在極短的時(shí)間內(nèi)做出交易決策,并執(zhí)行交易指令。與傳統(tǒng)的基于CPU的交易系統(tǒng)相比,F(xiàn)PGA開(kāi)發(fā)板能夠***縮短交易延遲,提高交易效率,幫助金融機(jī)構(gòu)在激烈的市場(chǎng)競(jìng)爭(zhēng)中搶占先機(jī)。同時(shí),開(kāi)發(fā)板的可重構(gòu)特性使得金融機(jī)構(gòu)能夠根據(jù)市場(chǎng)變化和交易策略的調(diào)整,對(duì)交易算法進(jìn)行修改和優(yōu)化,實(shí)現(xiàn)交易系統(tǒng)的靈活升級(jí),更好地適應(yīng)復(fù)雜多變的金融市場(chǎng)環(huán)境,提升金融交易的智能化和化水平。 福建專注FPGA開(kāi)發(fā)板設(shè)計(jì)數(shù)字藝術(shù)創(chuàng)作借助 FPGA 開(kāi)發(fā)板,實(shí)現(xiàn)互動(dòng)裝置的獨(dú)特創(chuàng)意設(shè)計(jì)。

FPGA 開(kāi)發(fā)板在數(shù)字藝術(shù)創(chuàng)作領(lǐng)域?yàn)樗囆g(shù)家?guī)?lái)了新的創(chuàng)作媒介與表現(xiàn)形式。藝術(shù)家可以利用開(kāi)發(fā)板實(shí)現(xiàn)互動(dòng)藝術(shù)裝置的設(shè)計(jì)。通過(guò)在 FPGA 上編寫邏輯程序,控制燈光、聲音、機(jī)械運(yùn)動(dòng)等元素,創(chuàng)造出獨(dú)特的藝術(shù)效果。例如,開(kāi)發(fā)板連接 LED 燈帶,根據(jù)音樂(lè)節(jié)奏或觀眾的動(dòng)作實(shí)時(shí)改變燈光的顏色、亮度與閃爍頻率,營(yíng)造出富有動(dòng)感與互動(dòng)性的燈光藝術(shù)氛圍;或者控制機(jī)械結(jié)構(gòu)的運(yùn)動(dòng),結(jié)合光影效果,呈現(xiàn)出動(dòng)態(tài)的藝術(shù)造型。開(kāi)發(fā)板的可編程性使得藝術(shù)家能夠自由地實(shí)現(xiàn)自己的創(chuàng)意,將數(shù)字技術(shù)與藝術(shù)創(chuàng)作相結(jié)合,打破傳統(tǒng)藝術(shù)創(chuàng)作的局限,為觀眾帶來(lái)全新的藝術(shù)體驗(yàn),推動(dòng)數(shù)字藝術(shù)的創(chuàng)新與發(fā)展。

FPGA 開(kāi)發(fā)板的軟件生態(tài)同樣豐富,為開(kāi)發(fā)者提供了的支持。在開(kāi)發(fā)工具方面,Xilinx 的 Vivado 軟件是一款功能強(qiáng)大的開(kāi)發(fā)套件。它集成了設(shè)計(jì)輸入、綜合、實(shí)現(xiàn)和調(diào)試等一系列功能。開(kāi)發(fā)者可以通過(guò)硬件描述語(yǔ)言,如 Verilog 或 VHDL,在 Vivado 中進(jìn)行設(shè)計(jì)輸入,將自己的電路設(shè)計(jì)思路轉(zhuǎn)化為代碼形式。綜合工具會(huì)將這些代碼轉(zhuǎn)化為門級(jí)網(wǎng)表,映射到 FPGA 芯片的邏輯資源上。實(shí)現(xiàn)過(guò)程則負(fù)責(zé)將網(wǎng)表布局到 FPGA 芯片位置,并完成布線,確保信號(hào)能夠準(zhǔn)確傳輸。功能允許開(kāi)發(fā)者在實(shí)際硬件實(shí)現(xiàn)之前,對(duì)設(shè)計(jì)進(jìn)行功能驗(yàn)證,通過(guò)設(shè)置輸入激勵(lì),觀察輸出結(jié)果,檢查設(shè)計(jì)是否符合預(yù)期,降低了開(kāi)發(fā)過(guò)程中的錯(cuò)誤。調(diào)試工具則在硬件實(shí)現(xiàn)后,幫助開(kāi)發(fā)者解決可能出現(xiàn)的問(wèn)題,例如通過(guò)邏輯分析儀觀察內(nèi)部信號(hào)的變化,找出邏輯錯(cuò)誤或時(shí)序問(wèn)題。同時(shí),Vivado 還提供了豐富的 IP 核資源,開(kāi)發(fā)者可以直接調(diào)用這些預(yù)先設(shè)計(jì)好的功能模塊,如數(shù)字信號(hào)處理模塊、通信協(xié)議模塊等,極大地縮短了開(kāi)發(fā)周期,提高了開(kāi)發(fā)效率,讓開(kāi)發(fā)者能夠更專注于系統(tǒng)級(jí)的設(shè)計(jì)與創(chuàng)新。FPGA 開(kāi)發(fā)板的可編程邏輯,賦予硬件設(shè)計(jì)無(wú)限可能。

FPGA 開(kāi)發(fā)板的功耗管理是開(kāi)發(fā)者需要關(guān)注的重要方面。在便攜式設(shè)備或電池供電的應(yīng)用場(chǎng)景中,降低開(kāi)發(fā)板功耗尤為關(guān)鍵。開(kāi)發(fā)者可通過(guò)優(yōu)化 FPGA 邏輯設(shè)計(jì),減少不必要的邏輯翻轉(zhuǎn),降低芯片動(dòng)態(tài)功耗。合理配置開(kāi)發(fā)板外設(shè),在不使用時(shí)將其設(shè)置為低功耗模式,進(jìn)一步降低系統(tǒng)功耗。部分開(kāi)發(fā)板提供專門的功耗管理模塊,幫助開(kāi)發(fā)者監(jiān)控與調(diào)節(jié)功耗,通過(guò)軟件設(shè)置實(shí)現(xiàn)不同的功耗管理策略。良好的功耗管理使 FPGA 開(kāi)發(fā)板能夠在低功耗狀態(tài)下穩(wěn)定運(yùn)行,滿足特定應(yīng)用場(chǎng)景對(duì)功耗的嚴(yán)格要求,延長(zhǎng)設(shè)備續(xù)航時(shí)間。FPGA 開(kāi)發(fā)板助力無(wú)線通信設(shè)備,實(shí)現(xiàn)高效信號(hào)收發(fā)與處理。湖北XilinxFPGA開(kāi)發(fā)板語(yǔ)法

選擇 FPGA 開(kāi)發(fā)板后,可參考實(shí)際用戶評(píng)價(jià)或先租賃進(jìn)行短期測(cè)試,以此驗(yàn)證其是否契合需求。江西安路FPGA開(kāi)發(fā)板芯片

FPGA 開(kāi)發(fā)板的硬件調(diào)試工具是開(kāi)發(fā)者定位與解決問(wèn)題的重要幫手。邏輯分析儀能夠?qū)崟r(shí)采集 FPGA 內(nèi)部信號(hào),幫助開(kāi)發(fā)者觀察信號(hào)的時(shí)序與狀態(tài)。在調(diào)試數(shù)字電路設(shè)計(jì)時(shí),通過(guò)邏輯分析儀可查看信號(hào)的變化情況,判斷邏輯設(shè)計(jì)是否符合預(yù)期,從而定位邏輯錯(cuò)誤。示波器可用于測(cè)量 FPGA 輸出的模擬信號(hào)或數(shù)字信號(hào)波形,檢查信號(hào)的質(zhì)量與完整性,如判斷信號(hào)是否存在畸變、噪聲等問(wèn)題。此外,部分開(kāi)發(fā)板配備板載調(diào)試器,支持在線調(diào)試功能,開(kāi)發(fā)者可在不脫離開(kāi)發(fā)板運(yùn)行環(huán)境的情況下,進(jìn)行斷點(diǎn)設(shè)置、變量查看等操作,快速定位軟件代碼中的問(wèn)題,提高調(diào)試效率,加速開(kāi)發(fā)進(jìn)程。江西安路FPGA開(kāi)發(fā)板芯片

- 河南嵌入式FPGA學(xué)習(xí)視頻 2025-07-20

- 河北嵌入式FPGA入門 2025-07-20

- 遼寧國(guó)產(chǎn)FPGA工業(yè)模板 2025-07-20

- 江蘇安路FPGA設(shè)計(jì) 2025-07-20

- 天津核心板FPGA特點(diǎn)與應(yīng)用 2025-07-20

- 廣東安路FPGA 2025-07-20

- 江蘇學(xué)習(xí)FPGA工程師 2025-07-20

- 山東學(xué)習(xí)FPGA芯片 2025-07-20

- 廣東工控板FPGA工程師 2025-07-20

- 深圳國(guó)產(chǎn)FPGA模塊 2025-07-20

- 普陀區(qū)自動(dòng)化電子元器件 2025-07-20

- 宿遷全自動(dòng)噴砂線訂購(gòu) 2025-07-20

- 湖州小功率三極管供應(yīng) 2025-07-20

- 江蘇通用充電樁銷售銷售價(jià)格 2025-07-20

- 英威騰GD200A-02變頻器故障 2025-07-20

- 長(zhǎng)寧區(qū)本地整流橋圖片 2025-07-20

- 華東全拆分放大器基本原理 2025-07-20

- 楊浦區(qū)半導(dǎo)體igbt模塊 2025-07-20

- 福建萬(wàn)兆多模光模塊 2025-07-20

- 浙江IATF16949成型件設(shè)計(jì) 2025-07-20