FPGA開發(fā)板在金融領域的應用逐漸興起,為金融科技的發(fā)展帶來新的機遇。在高頻交易系統(tǒng)中,時間就是金錢,對數(shù)據(jù)處理速度和實時性要求極高。FPGA開發(fā)板憑借其高速并行處理能力,能夠獲取金融市場的實時行情數(shù)據(jù)。通過預先編寫的交易算法,開發(fā)板對這些數(shù)據(jù)進行實時分析和處理,在極短的時間內做出交易決策,并執(zhí)行交易指令。與傳統(tǒng)的基于CPU的交易系統(tǒng)相比,F(xiàn)PGA開發(fā)板能夠***縮短交易延遲,提高交易效率,幫助金融機構在激烈的市場競爭中搶占先機。同時,開發(fā)板的可重構特性使得金融機構能夠根據(jù)市場變化和交易策略的調整,對交易算法進行修改和優(yōu)化,實現(xiàn)交易系統(tǒng)的靈活升級,更好地適應復雜多變的金融市場環(huán)境,提升金融交易的智能化和化水平。 FPGA 開發(fā)板在雷達系統(tǒng)中,完成目標檢測與回波分析。FPGA開發(fā)板基礎

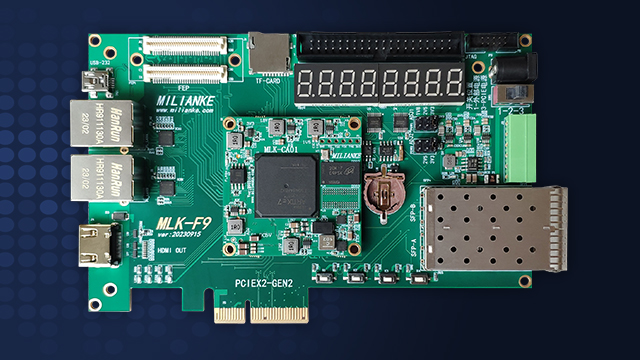

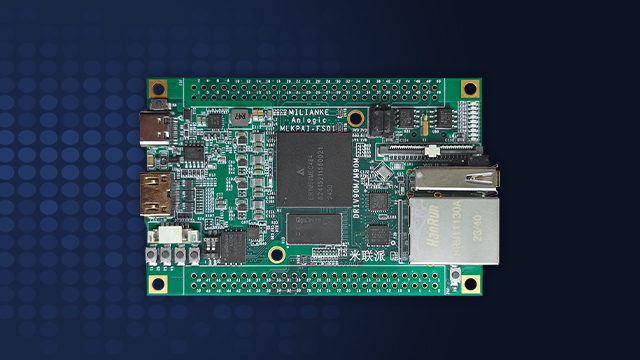

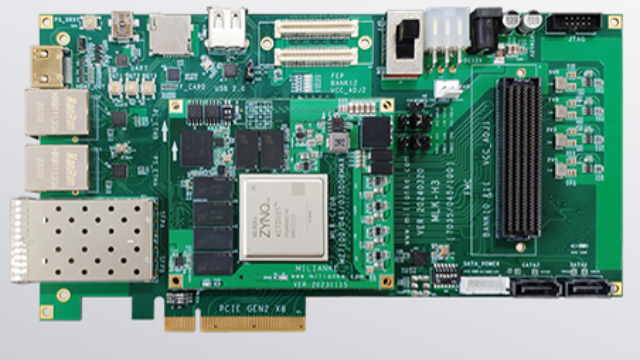

FPGA開發(fā)板作為數(shù)字電路設計的重要實踐平臺,其硬件架構融合了多種關鍵組件。以常見的XilinxArtix-7系列開發(fā)板為例,F(xiàn)PGA芯片是整個系統(tǒng)的關鍵器件,像XC7A100T型號芯片,擁有豐富的邏輯單元、DSP切片和BlockRAM資源,能夠滿足復雜數(shù)字系統(tǒng)的設計需求。開發(fā)板上配備的電源管理模塊,通過多級電壓轉換電路,為FPGA芯片及其他外設提供穩(wěn)定的供電,例如將外部輸入的5V電壓轉換為、等不同電壓等級,確保各部件正常運行。復位電路在啟動或異常情況下能回到初始狀態(tài),晶振電路為系統(tǒng)提供精確的時鐘信號,使FPGA內部邏輯單元能夠按照預定節(jié)奏工作。此外,開發(fā)板還集成了豐富的接口,包括USB、以太網、SPI、I2C等,方便與外部設備進行數(shù)據(jù)交互和通信,這些硬件資源共同構成了FPGA開發(fā)板穩(wěn)定運行的基礎環(huán)境。 湖北賽靈思FPGA開發(fā)板芯片F(xiàn)PGA 開發(fā)板的多層次開發(fā)環(huán)境,為不同水平開發(fā)者提供便利。

FPGA開發(fā)板在電子競賽領域展現(xiàn)出獨特優(yōu)勢。電子競賽題目往往對硬件的靈活性與功能實現(xiàn)有較高要求,F(xiàn)PGA開發(fā)板憑借其可編程特性,能夠快速響應不同競賽需求。在智能車競賽中,參賽團隊使用開發(fā)板處理傳感器采集到的賽道信息,如光電傳感器檢測賽道黑線、陀螺儀獲取車身姿態(tài)數(shù)據(jù)等。通過編寫相應算法對數(shù)據(jù)進行分析處理,進而驅動電機實現(xiàn)智能車在賽道上的行駛。在電子設計競賽中,開發(fā)板可用于實現(xiàn)信號處理、數(shù)據(jù)采集、無線通信等多個功能模塊,滿足競賽題目多樣化的需求。參賽者通過對開發(fā)板的不斷編程與調試,優(yōu)化系統(tǒng)性能,提升作品競爭力,使FPGA開發(fā)板成為電子競賽中不可或缺的開發(fā)平臺。

FPGA 開發(fā)板的功耗管理是開發(fā)者需要關注的重要方面。在便攜式設備或電池供電的應用場景中,降低開發(fā)板功耗尤為關鍵。開發(fā)者可通過優(yōu)化 FPGA 邏輯設計,減少不必要的邏輯翻轉,降低芯片動態(tài)功耗。合理配置開發(fā)板外設,在不使用時將其設置為低功耗模式,進一步降低系統(tǒng)功耗。部分開發(fā)板提供專門的功耗管理模塊,幫助開發(fā)者監(jiān)控與調節(jié)功耗,通過軟件設置實現(xiàn)不同的功耗管理策略。良好的功耗管理使 FPGA 開發(fā)板能夠在低功耗狀態(tài)下穩(wěn)定運行,滿足特定應用場景對功耗的嚴格要求,延長設備續(xù)航時間。不同廠商的 FPGA 開發(fā)板各具特色,滿足多樣化應用場景需求。

FPGA 開發(fā)板的升級與拓展能力為其應用帶來更多可能性。隨著技術發(fā)展,開發(fā)者可通過更新 FPGA 的配置文件,為開發(fā)板添加新功能或優(yōu)化現(xiàn)有功能。許多開發(fā)板預留拓展接口,開發(fā)者可根據(jù)項目需求添加額外功能模塊。如在圖像識別項目中,添加攝像頭模塊獲取圖像數(shù)據(jù);在定位導航項目中,接入 GPS 模塊獲取位置信息。這種升級與拓展能力使 FPGA 開發(fā)板能夠適應不斷變化的應用需求,延長開發(fā)板的使用壽命,提高其性價比,在不同項目與應用場景中持續(xù)發(fā)揮重要作用,滿足開發(fā)者多樣化的開發(fā)需求。若要進行高速數(shù)據(jù)傳輸,帶有 SFP + 光纖接口、支持高速協(xié)議的 FPGA 開發(fā)板會是理想之選。湖北初學FPGA開發(fā)板論壇

邊緣計算領域,F(xiàn)PGA 開發(fā)板實現(xiàn)數(shù)據(jù)的本地高效處理與分析。FPGA開發(fā)板基礎

FPGA開發(fā)板在物聯(lián)網網關的設計中發(fā)揮著關鍵作用。物聯(lián)網網關作為連接物聯(lián)網設備與互聯(lián)網的橋梁,需要具備強大的數(shù)據(jù)處理與通信能力。FPGA開發(fā)板可通過多種接口連接各類物聯(lián)網傳感器與設備,如Wi-Fi、藍牙、ZigBee等無線接口,以及RS232、RS485等串口接口,實現(xiàn)對不同協(xié)議、不同類型設備的數(shù)據(jù)采集。對采集到的數(shù)據(jù)進行預處理,如數(shù)據(jù)過濾、格式轉換等,然后通過以太網接口或4G/5G通信模塊將數(shù)據(jù)上傳至云端服務器。同時,開發(fā)板還能接收來自云端的指令,將指令轉發(fā)給相應的物聯(lián)網設備。此外,開發(fā)板可在本地運行邊緣計算算法,對部分數(shù)據(jù)進行實時分析與處理,減少數(shù)據(jù)傳輸量,降低對云端服務器的依賴,提高物聯(lián)網系統(tǒng)的響應速度與可靠性,推動物聯(lián)網技術的廣泛應用與發(fā)展。 FPGA開發(fā)板基礎