常州RFFE分析儀售價

才能符合此表達式。換句話說,在ADDR等于1000的同時DATA等于2000。因此,如果要在同時發生兩個事件時觸發,則應使用布爾邏輯表達式。常見錯誤是應使用布爾邏輯表達式時嘗試使用兩個序列步驟,或者應使用兩個序列步驟時嘗試使用布爾邏輯表達式。當多個事件同時發生時使用布爾邏輯表達式,而在一個事件接著一個事件發生時使用多個序列步驟。分支:分支類似于C編程語言中的Switch語句和Basic中的SelectCase語句。分支可提供測試多個sADDR”。多數邏輯分析儀還支持“notinrange”功能。范圍是一種方便的快捷方式,因此您無需指定“ADDR>=1000andADDR<=>標志:標志是用于從一個模塊向另一個模塊發送信號的布爾變量。當某種情況在某一模塊中發生而稍后被另一模塊測試時可以設置標志。在下面的示例中,標志1用于跟蹤在模塊1的觸發序列中發生的情況,如,如果想在ADDR=1000第5次出現時觸發,可以將觸發設置為:IfADDR=1000occurs5timesthenTrigger全局計數器類似于整數變量。全局計數器比發生計數器更靈活,因為它們可用于為復雜事件(例如一個時鐘沿后跟另一時鐘沿的事件)計數。可以增加、測試和重新設置全局計數器。默認情況下,全局計數器以零開頭并且不需要重新設置。協議分析儀/邏輯訓練器廠家直銷就找歐奧!常州RFFE分析儀售價

除非已在觸發序列中使用了它們。一般情況下,如果可能的話,應使用發生計數器代替全局計數器,原因是發生計數器的用法比較簡單,而且全局計數器的數量有限。定時器:定時器用于檢查事件之間消耗的時間。例如,如果想在出現一個時鐘沿后的500ns內出現另一個時鐘沿的情況下引發觸發,請使用定時器。使用定時器時要記住的關鍵一點是:先啟動定時器,然后再對其進行測試。換句話說,定時器無法自動啟動。設置定時器的關鍵是確定在何種情況下進行啟動和測試。存儲限定:存儲限定用于確定應該存儲(即,存入內存)還是丟棄已獲得的樣本。這可以避免不需要的樣本占用邏輯分析儀內存。設置存儲限定簡單的方法是設置“默認存儲”。默認存儲表示“如果未經序列步驟指定,則進行存儲”。例如,可能只想在ADDR的范圍為1000到2000時存儲樣本,那么就應將“默認存儲”設置為:ADDRInRange1000to2000默認情況下,“默認存儲”設置為存儲所有已獲得的樣本。也可以將“默認存儲”設置為不存儲任何樣本,這意味著除非某序列步驟覆蓋該默認存儲,否則將不存儲任何樣本。序列步驟存儲限定意味著在某個特定的序列步驟內只存儲特定的樣本。這意味著在使用GoTo(轉到)或Trigger。梅州UFS分析儀品牌JTAG協議分析儀/訓練器找歐奧!

UFS總線協議分析儀測試解決方案不會收到EAR進出口方面的管制。同時還有代理其他總類的協議分析儀,包括嵌入式設備用的SDIO協議分析儀,QSPI協議分析儀及訓練器,I3C協議分析儀及訓練器,RFFE協議分析儀及訓練器等等。我司還有代理SPMI協議分析儀及訓練器,車載以太網分析儀,以及各種相關的基于示波器的解碼軟件和SI測試軟件。同時,歐奧電子也有提供高難度焊接,以及高速信號,如UFS,DDR3/DDR4,USBtypeC等高速協議抓取和分析的服務。比較幀類型:可自行選擇;5、數據:可輸入對應幀類型數據的十進制,十六進制,八進制。設置效果如圖6所示:圖6幀查找屬性設置七、解碼數據準確定位完成設置,則可以通過查找具體的查找類型進行顯示,效果如圖7所示:圖7查找結果顯示此次查找共有68個查找結果,可通過如下操作觀測每一個查找結果,效果如圖8所示:圖8查找結果數據分析ZLG致遠電子邏輯分析儀具有超大容量存儲、智能過濾存儲、高保真不間斷實時記錄、高效的協議分析平臺、觸發搜索多樣化、靈活的參數測量,能夠定位系統運行出錯時的特定波形數據。針對數字電路的開發和測試人員可以用邏輯分析儀對電路進行精確的狀態或時序分析,以檢測分析電路設計中的錯誤,從而迅速定位。

邏輯分析儀基礎邏輯分析儀是一種類似于示波器的波形測試設備,它可以監測硬件電路工作時的邏輯電平(高或低),并加以存儲,用圖形的方式直觀地表達出來,便于用戶檢測和分析電路設計(硬件設計和軟件設計)中的錯誤。邏輯分析儀是設計中不可缺少的電子測試設備,通過它可以迅速地定位錯誤、解決問題、達到事半功倍的效果。一、邏輯分析儀的產生和發展20世紀70年代初研制出微處理器,出現4位和8位總線,傳統示波器的雙通道輸入無法滿足8bit的觀察。微處理器和存儲器的測試需要不同于時域和頻域儀器,所以數域測試儀器應運而生。當時的HP公司推出狀態分析儀和Biomation公司推出定時分析儀(兩者初很不相同)之后不久,用戶開始接受這種數域測試儀器作為終解決數字電路測試的手段,不久狀態分析儀與定時分析儀合并成邏輯分析儀。20世紀80年代后期,邏輯分析儀變得更加復雜,使用起來也更加困難。例如,引入多電平樹形觸發,以應付條件語句如IF、THEN、ELSE等復雜事件。這類組合觸發必然更加靈活,同時對大多數用戶來說就不是那樣容易掌握了。邏輯分析儀的基本發展趨勢是計算機與儀器的不斷融合。在PC機平臺上使用Windows,只要給定正確的軟件和相關工具。SDIO協議分析儀/訓練器找歐奧!

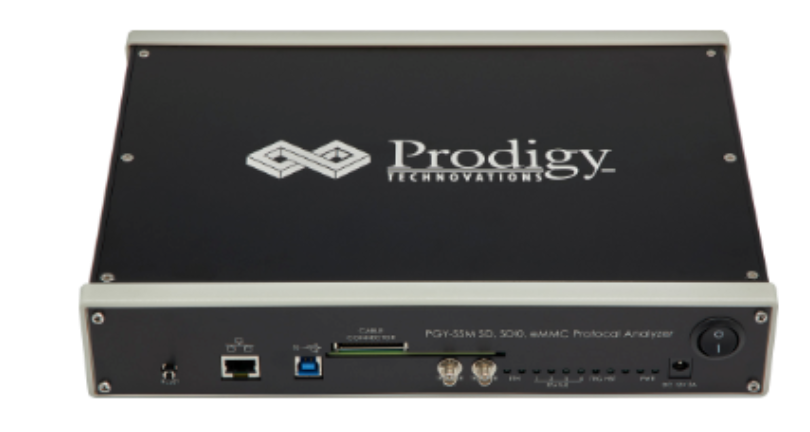

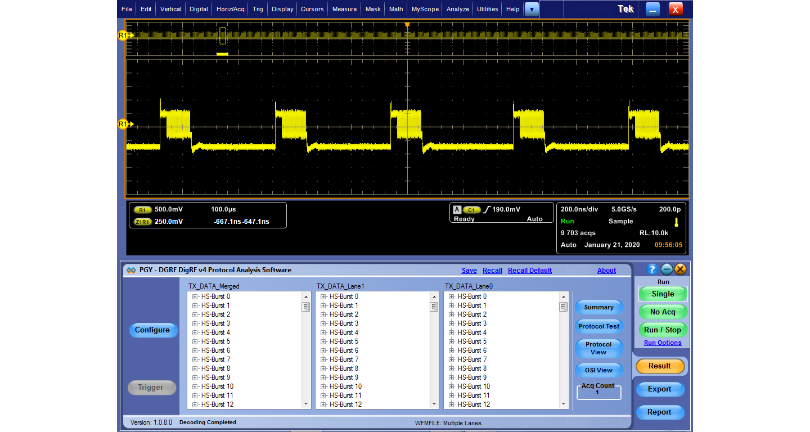

然后依次是AT24C16的標識0xA2,寫入地址0x00,數據0x10,0x27等。由于寫入以字節為單位,因此0x2710=10000,表明采樣成功。將鼠標放在波形上,點擊左鍵,實現zoomin功能。結果見圖3,在“start”條件后,在SCL的8個連續脈沖的高電平處,SDA對應的信號為10100010,即0xA2,第9個脈沖高電平處為0,是ACK標志。以上簡單介紹了用邏輯分析儀進行I2C分析的過程,可以看到操作起來非常簡單。下面再介紹利用邏輯分析儀采樣三相交流電機驅動器的6路PWM波形。硬件連接?先將邏輯分析儀的GND與目標板的GND連接,讓二者共地,見圖5。2.?選擇需要采樣的信號,這里就是單片機6路PWM波形的輸出引腳,將其接入邏輯分析儀的通道1(Input1)至通道6(Input6),并且把通道的名字改為Utop、Ubottom、Vtop、Vbottom、Wtop、WBottom,分別三路輸出的上下橋臂。3.?將邏輯分析儀和電腦USB口連接,windows會識別該設備,并在屏幕右下角顯示USB設備標識。軟件使用?運行Saleae軟件,此時邏輯分析儀的硬件已經與電腦相連,軟件會顯示[Connected]。2.?設置采樣數量和速度,PWM的頻率為15kHz,這里設置為2MSamples@4MHz的速度。3.?設置觸發條件。歐奧電子是Prodigy在中國區的官方授權合作伙伴。SDIO協議分析儀/訓練器廠家只找歐奧,服務好!常州UART分析儀那家好

SD協議分析儀/訓練器找歐奧!常州RFFE分析儀售價

我們會找到信號與上升的Vref值交叉的位置。如果Vref升至足夠高,信號的頂部軌跡將通過Vref,我們便會看到眼的頂端。再將Vref升高一點會導致Vcomp保持在Vlo,表示信號不會升至該電之,將Vref移至零以下會看到眼的下半部。eyescan/eyefinder顯示窗口會在每個信號的eyescan圖下方顯示eyefinder交疊部分,以此顯示eyefinder與eyescan之間的這一關系。通過在eyescan圖中將Vth水平線向上和向下移動,可以獲得距離眼中心該偏移量位置處的eyefinder視圖。無論用戶界面中的閾值如何設置,邏輯分析儀的差分輸入將始終應用于接收器。這意味著可通過將電壓閾值手動設置為非零值允許在差分對中使用公共模式電壓。如果信號擺幅中心與地線差距于100mV,eyescan將自動執行此操作。邏輯分析儀的觸發設置邏輯分析儀觸發非常困難,而且還需花費量時間。假設如果知道如何編程,則應該可以毫不費力地設置邏輯分析儀觸發。然而,這是不可能的,因為許多概念對邏輯分析來說都是的。本節的目的就是介紹這些主要概念及如何有效地使用它們。傳送帶類比:我們可以將邏輯分析儀的內存比作一條很長的傳送帶,而從被測設備(DUT)獲取的樣本就像是傳送帶上的箱子。新的箱子被放置在傳送帶一端。常州RFFE分析儀售價

- 天津分析儀費用 2025-07-08

- 連云港I3C協議分析儀那家好 2025-07-08

- 珠海I2C/SPI分析儀找哪家 2025-07-08

- 廣州EMMC協議分析儀報價 2025-07-08

- 湖州RFFE分析儀 2025-07-08

- 西安I2C/SPI分析儀找哪家 2025-07-08

- 長沙RFFE分析儀收費 2025-07-08

- 韶關I2C/SPI協議分析儀廠家 2025-07-08

- 杭州SDIO分析儀報價 2025-07-08

- 株洲RFFE協議分析儀 2025-07-08

- 數顯表面洛氏硬度計分析儀器 2025-07-08

- 寶山區國內儀器儀表維保 2025-07-08

- 帶PON功能OTDR西南代理 2025-07-08

- 杭州激光測距傳感器模塊 2025-07-08

- 山東316壓力表價格 2025-07-08

- 鹽城那種過熱蒸汽流量計商家 2025-07-08

- 有哪些多聯機集控批發廠家 2025-07-08

- 溫州電容薄膜真空計生產企業 2025-07-08

- 廣西特色服務稱重傳感器生產廠家 2025-07-08

- 榆林智能化溫室氣體監測平臺 2025-07-08