軟件測試UFS信號完整性測試M-PHY測試

UFS 信號完整性測試之信號質量評估參數

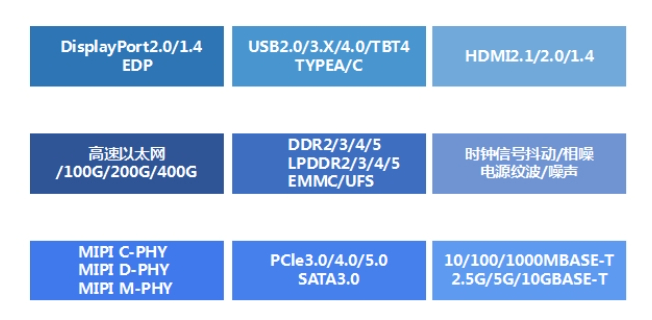

UFS 信號完整性測試依據多項信號質量評估參數。上升時間、下降時間反映信號變化快慢,過快或過慢都可能引發問題。信號噪聲影響信號清晰度,噪聲過大易使信號誤判。通過測量這些參數,能評估信號質量。例如,上升時間過長,信號沿變緩,可能導致數據傳輸速率下降。依據評估參數,可針對性優化信號傳輸,滿足 UFS 信號完整性要求。

UFS 信號完整性測試之物理層協議影響

UFS 使用 MIPI M-PHY 作為物理層協議,對信號完整性影響明顯。該協議支持高速差分信號傳輸,提高數據速率。但隨著速率提升,信號完整性挑戰增大。在測試中,要關注物理層協議規定的電氣特性、信號擺幅等。例如,減少信號擺幅雖能降低功耗,卻可能影響信噪比。遵循物理層協議規范,優化信號傳輸,是保障 UFS 信號完整性的基礎。 UFS 信號完整性測試之信號完整性與抗振動性能?軟件測試UFS信號完整性測試M-PHY測試

UFS 信號完整性測試之不同版本 UFS 測試差異

不同版本 UFS 信號完整性測試有差異。UFS 4.0 比 UFS 3.1 傳輸速率更高,測試時對儀器帶寬、采樣率要求更嚴。UFS 4.0 需測試 23.2Gbps 速率下的信號,而 UFS 3.1 比較高 11.6Gbps 。高版本 UFS 對眼圖參數、抖動控制更苛刻。測試時需根據具體版本調整測試標準與儀器設置,確保測試符合對應版本的技術規范。

UFS 信號完整性測試之供應鏈測試協作

UFS 供應鏈中,各環節測試協作很重要。芯片廠商、板卡制造商、整機廠商需統一測試標準。芯片廠商提供芯片信號參數,板卡廠商測試板級信號完整性,整機廠商進行系統級測試。通過共享測試數據,及時發現設計、生產環節的信號問題。良好的協作能縮短產品研發周期,降低成本,確保蕞終產品 UFS 信號完整性達標。 軟件測試UFS信號完整性測試M-PHY測試UFS 信號完整性與傳輸線損耗?

UFS 信號完整性在 PCB 設計要點

PCB 設計對 UFS 信號完整性影響深遠。在布線方面,要確保傳輸線短而直,減少信號傳輸路徑上的彎折、過孔數量,降低信號反射和傳輸損耗。差分信號對需嚴格等長匹配,同一 Lane 內的 TX/RX 差分對長度偏差≤5mil ,組間偏差≤50mil ,保證信號同時到達接收端,避免時序錯位。信號下方應保留連續地平面,避免跨分割,為信號提供穩定參考。在布局上,UFS 芯片與相關元器件要緊密放置,縮短信號走線長度。同時,合理布置接地屏蔽過孔,隔離相鄰信號間的串擾。遵循這些 PCB 設計要點,能有效提升 UFS 信號完整性,保障系統性能。

UFS 信號完整性測試之信號完整性與抗振動性能

在車載、工業設備中,UFS 需具備抗振動能力,這與信號完整性相關。振動可能導致接口接觸不良、線路微形變,影響信號傳輸。測試時,通過振動臺模擬不同頻率、振幅的振動,監測信號參數變化。若振動中信號完整性明顯下降,需加固接口、優化線路固定方式。確保 UFS 在振動環境下信號穩定,是其在特殊領域應用的前提。

UFS 信號完整性測試之多通道同步測試要點

UFS 常采用多通道傳輸,多通道同步測試很重要。各通道信號需保持同步,否則會出現時序偏差,影響數據整合。測試時,用多通道示波器同時采集信號,分析通道間延遲。要求通道間延遲<0.1UI ,確保數據在接收端同步處理。若同步性差,需調整各通道線路長度、驅動能力,保證多通道信號協同傳輸,提升整體信號完整性。

UFS 信號完整性測試之信號質量優化?

UFS 信號完整性測試之自動化測試優勢

自動化測試在 UFS 信號完整性測試中優勢明顯。傳統手動測試效率低、易出錯,尤其在批量測試時。自動化測試通過編程控制儀器,可快速完成參數測量、數據記錄與分析。能在短時間內測試大量樣本,保證測試一致性。還可自動生成測試報告,便于追溯問題。采用自動化測試,能大幅提升 UFS 信號完整性測試效率與準確性,降低人工成本。

UFS 信號完整性測試之不同應用場景測試差異

UFS 在手機、汽車電子等不同場景應用,信號完整性測試有差異。手機對功耗敏感,測試需兼顧低功耗下的信號質量;汽車電子要求在 -40℃~125℃ 寬溫環境穩定,測試要模擬極端溫度。不同場景的電磁環境也不同,測試時電磁屏蔽措施需調整。針對場景特點設計測試方案,才能確保 UFS 在各領域都能可靠工作。 UFS 信號完整性測試工具介紹?軟件測試UFS信號完整性測試檢查

UFS 信號完整性測試之故障模擬測試方法?軟件測試UFS信號完整性測試M-PHY測試

UFS 信號完整性與時鐘信號關系

時鐘信號在 UFS 信號完整性中扮演關鍵角色。UFS 設備依靠時鐘信號來同步數據的發送與接收,確保數據在正確時刻被采樣、處理。穩定、精細的時鐘信號是保障信號完整性的基礎。若時鐘信號出現頻率偏差、抖動等問題,會使數據傳輸的時序錯亂。比如時鐘頻率漂移,會導致發送端和接收端數據速率不一致,接收端無法在正確時刻采樣數據,引發誤碼;時鐘抖動則會增大數據傳輸的不確定性。因此,在 UFS 系統設計中,要精心設計時鐘電路,采用高精度時鐘源,做好時鐘信號的隔離、濾波,保證時鐘信號穩定,為 UFS 信號完整性提供堅實支撐。 軟件測試UFS信號完整性測試M-PHY測試

- 通信MIPID-PHY測試項目 2025-07-14

- 測試原理UFS信號完整性測試時鐘抖動測試 2025-07-14

- si信號完整性UFS信號完整性測試端口測試 2025-07-14

- 測試原理UFS信號完整性測試方案 2025-07-14

- si信號完整性UFS信號完整性測試M-PHY測試 2025-07-14

- 測試項目介紹UFS信號完整性測試一致性測試 2025-07-14

- 信號分析UFS信號完整性測試測試流程 2025-07-13

- 信息化UFS信號完整性測試信號眼圖 2025-07-13

- 信號完整性測試UFS信號完整性測試物理層測試 2025-07-13

- 數字接口測試系列UFS信號完整性測試檢查 2025-07-13

- 浙江測溫裝置測溫管規格 2025-07-14

- 東莞螺紋防水呼吸器一般多少錢 2025-07-14

- 重慶國產晶圓快速退火爐品牌 2025-07-14

- 廣東動力電池泄壓閥供應商 2025-07-14

- 進口光纖熔接機集采入圍 2025-07-14

- 湖北高穩定性準直鏡透鏡 2025-07-14

- 干線光纖熔接機聯系電話 2025-07-14

- 徐州鎧裝溫度傳感器哪家好 2025-07-14

- 上海人臉識別非球面透鏡 2025-07-14

- 加長型全自動洛氏硬度計FR-X1L現貨 2025-07-14