江西開發(fā)FPGA開發(fā)板基礎(chǔ)

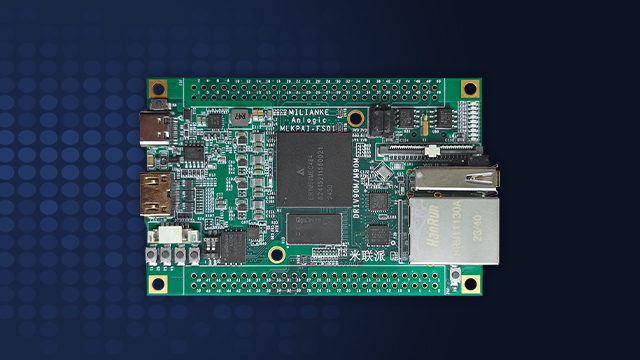

米聯(lián)客推出的開源 FPGA 低時延 ISP 圖像處理方案,聚焦于 FPGA 在圖像處理領(lǐng)域的高效應(yīng)用。該方案依托 MLK-H10-CK203/204 國產(chǎn)安路 FPGA 開發(fā)板,實現(xiàn)從 MIPI 接口采集攝像頭數(shù)據(jù),經(jīng) ISP 圖像算法處理后緩存至 DDR,由 HDMI 接口輸出。方案著重低延遲設(shè)計,契合自動駕駛、機器視覺、醫(yī)療內(nèi)窺鏡等對實時性要求極高的場景。米聯(lián)客不僅詳細(xì)闡述算法原理,還開源所有源碼與教程,助力客戶深入學(xué)習(xí)、靈活應(yīng)用,利用 FPGA 并行處理、可定制化硬件邏輯與低延遲特性,提升圖像處理效率與質(zhì)量。若要進(jìn)行高速數(shù)據(jù)傳輸,帶有 SFP + 光纖接口、支持高速協(xié)議的 FPGA 開發(fā)板會是理想之選。江西開發(fā)FPGA開發(fā)板基礎(chǔ)

FPGA開發(fā)板在汽車電子領(lǐng)域扮演著重要角色,推動著汽車智能化的發(fā)展進(jìn)程。在汽車的自動駕駛系統(tǒng)中,開發(fā)板用于處理來自各種傳感器的數(shù)據(jù),如攝像頭、雷達(dá)、激光雷達(dá)等。這些傳感器會實時采集汽車周圍環(huán)境的信息,F(xiàn)PGA開發(fā)板以高速并行處理的方式,對這些數(shù)據(jù)進(jìn)行融合和分析,通過復(fù)雜的算法識別道路、車輛、行人等目標(biāo)物體,為自動駕駛決策提供準(zhǔn)確的依據(jù)。例如,開發(fā)板根據(jù)傳感器數(shù)據(jù)判斷前方車輛的距離和速度,結(jié)合自身車輛的行駛狀態(tài),決策是否需要加速、減速或保持當(dāng)前速度。在汽車的車身系統(tǒng)中,開發(fā)板可實現(xiàn)對車輛燈光、車窗、門鎖等設(shè)備的智能。通過與汽車的CAN總線通信,開發(fā)板接收來自車內(nèi)網(wǎng)絡(luò)的指令,實現(xiàn)對車身設(shè)備的集中管理和智能化操作,提高汽車的安全性、舒適性和智能化程度,為未來汽車的發(fā)展注入強大的技術(shù)動力。 上海FPGA開發(fā)板套件FPGA 開發(fā)板的開源項目,促進(jìn)技術(shù)共享與開發(fā)者之間的交流合作。

FPGA開發(fā)板的軟件生態(tài)同樣豐富,為開發(fā)者提供了的支持。在開發(fā)工具方面,Xilinx的Vivado軟件是一款功能強大且使用的開發(fā)套件。它集成了設(shè)計輸入、綜合、實現(xiàn)、仿真和調(diào)試等一系列功能。開發(fā)者可以通過硬件描述語言,如Verilog或VHDL,在Vivado中進(jìn)行設(shè)計輸入,將自己的電路設(shè)計思路轉(zhuǎn)化為代碼形式。綜合工具會將這些代碼轉(zhuǎn)化為門級網(wǎng)表,映射到FPGA芯片的邏輯資源上。實現(xiàn)過程則負(fù)責(zé)將網(wǎng)表布局到FPGA芯片的具置,并完成布線,確保信號能夠準(zhǔn)確傳輸。仿真功能允許開發(fā)者在實際硬件實現(xiàn)之前,對設(shè)計進(jìn)行功能驗證,通過設(shè)置輸入激勵,觀察輸出結(jié)果,檢查設(shè)計是否符合預(yù)期,降低了開發(fā)過程中的錯誤風(fēng)險。調(diào)試工具則在硬件實現(xiàn)后,幫助開發(fā)者定位和解決可能出現(xiàn)的問題,例如通過邏輯分析儀觀察內(nèi)部信號的變化,找出邏輯錯誤或時序問題。同時,Vivado還提供了豐富的IP核資源,開發(fā)者可以直接調(diào)用這些預(yù)先設(shè)計好的功能模塊,如數(shù)字信號處理模塊、通信協(xié)議模塊等,極大地縮短了開發(fā)周期,提高了開發(fā)效率,讓開發(fā)者能夠更專注于系統(tǒng)級的設(shè)計與創(chuàng)新。

FPGA開發(fā)板在教育領(lǐng)域扮演著越來越重要的角色,成為數(shù)字電路和嵌入式系統(tǒng)教學(xué)的重要工具。通過FPGA開發(fā)板,學(xué)生和學(xué)習(xí)者可以實踐性地理解數(shù)字邏輯設(shè)計的原理,掌握HDL編程的技巧,并加深對現(xiàn)代電子系統(tǒng)的理解。許多高校和培訓(xùn)機構(gòu)已經(jīng)將FPGA開發(fā)板納入課程體系,幫助學(xué)生提升實際操作能力和創(chuàng)新能力。此外,F(xiàn)PGA開發(fā)板的豐富資源和開源社區(qū)也為學(xué)習(xí)者提供了大量的教程和項目實例,進(jìn)一步降低了學(xué)習(xí)門檻,促進(jìn)了電子工程專業(yè)人才的培養(yǎng)。虛擬現(xiàn)實設(shè)備中,F(xiàn)PGA 開發(fā)板保障畫面流暢與交互體驗。

基于FPGA開發(fā)板進(jìn)行項目開發(fā)時,軟件工具鏈起著關(guān)鍵作用。以Altera(現(xiàn)Intel)的QuartusPrime軟件為例,其提供了完整的FPGA開發(fā)流程支持。在設(shè)計輸入階段,開發(fā)者既可以使用硬件描述語言Verilog或VHDL編寫代碼,描述電路的邏輯功能;也可以采用原理圖輸入方式,通過圖形化的方式搭建電路模塊,直觀展示設(shè)計架構(gòu)。完成設(shè)計輸入后,QuartusPrime的綜合功能會將代碼或原理圖轉(zhuǎn)換為門級網(wǎng)表,針對目標(biāo)FPGA芯片的邏輯資源進(jìn)行優(yōu)化映射。接著是布局布線環(huán)節(jié),軟件根據(jù)芯片的物理結(jié)構(gòu),合理安排邏輯單元的位置,并完成各單元之間的連線,確保信號傳輸?shù)臏?zhǔn)確性與穩(wěn)定性。通過編程下載功能,將生成的配置文件燒錄到FPGA開發(fā)板中,使設(shè)計在硬件上得以實現(xiàn)。同時,該軟件還提供了仿真功能,方便開發(fā)者在硬件實現(xiàn)前對設(shè)計進(jìn)行功能驗證,減少開發(fā)過程中的錯誤與風(fēng)險。 科研實驗時,F(xiàn)PGA 開發(fā)板為新技術(shù)驗證與算法測試提供可靠硬件平臺。天津FPGA開發(fā)板資料下載

FPGA 開發(fā)板的高速數(shù)據(jù)處理,滿足實時性應(yīng)用需求。江西開發(fā)FPGA開發(fā)板基礎(chǔ)

對于 使用FPGA 開發(fā)板的開發(fā)者而言,良好的代碼管理與版本控制習(xí)慣至關(guān)重要。隨著項目推進(jìn),代碼規(guī)模不斷增大,合理的代碼管理可提高開發(fā)效率,便于團隊協(xié)作與代碼維護。開發(fā)者使用版本控制工具,如 Git,對代碼進(jìn)行管理,記錄代碼修改歷史,方便追溯與回滾。遵循代碼規(guī)范,進(jìn)行模塊化設(shè)計,提高代碼可讀性與可復(fù)用性。不同功能模塊編寫代碼,通過接口進(jìn)行數(shù)據(jù)交互,降低代碼耦合度,使項目后續(xù)擴展與維護更加容易,保障項目長期穩(wěn)定發(fā)展。江西開發(fā)FPGA開發(fā)板基礎(chǔ)

常州米聯(lián)客信息科技有限公司,自2017年5月11日創(chuàng)立起,便在FPGA和SOC技術(shù)應(yīng)用領(lǐng)域不斷探索前行,逐步構(gòu)建起完善的技術(shù)體系和產(chǎn)品生態(tài)。公司具備專業(yè)的技術(shù)研發(fā)能力,從硬件設(shè)計到軟件生態(tài)開發(fā),形成了全技術(shù)棧的研發(fā)優(yōu)勢。在硬件產(chǎn)品方面,米聯(lián)客的生態(tài)產(chǎn)品覆蓋國際大廠品牌AMD、ALTERA,以及國內(nèi)的安路FPGA、龍芯中科、瑞芯微等品牌。公司的核心板模塊作為重點產(chǎn)品,在設(shè)計上充分考慮了不同行業(yè)的需求,具備高性能、低功耗、高可靠性等特點。同時,公司配套研發(fā)的軟件生態(tài)解決方案,能夠與硬件模塊無縫對接,為客戶提供一體化的解決方案。在實際應(yīng)用場景中,米聯(lián)客的產(chǎn)品和方案發(fā)揮著重要作用。在科研驗證場景下,為科研人員提供了靈活且可靠的實驗平臺,加速科研項目的推進(jìn);在工業(yè)自動化生產(chǎn)中,提高了生產(chǎn)設(shè)備的智能化水平和生產(chǎn)效率;在儀表儀器的設(shè)計制造中,提升了儀器的測量精度和穩(wěn)定性;在醫(yī)療產(chǎn)品的研發(fā)和生產(chǎn)中,為醫(yī)療設(shè)備的創(chuàng)新提供了技術(shù)保障;在機器視覺和自動駕駛領(lǐng)域,通過精細(xì)的數(shù)據(jù)處理和分析,助力相關(guān)技術(shù)實現(xiàn)突破。米聯(lián)客正通過不斷創(chuàng)新,推動各行業(yè)的技術(shù)升級和發(fā)展。

- 北京了解FPGA開發(fā)板芯片 2025-07-10

- 吉林安路開發(fā)板FPGA開發(fā)板學(xué)習(xí)步驟 2025-07-10

- 多功能FPGA定制項目解決方案 2025-07-10

- 安徽安路FPGA開發(fā)板平臺 2025-07-09

- 中國臺灣ZYNQFPGA開發(fā)板代碼 2025-07-09

- 重慶專注FPGA開發(fā)板芯片 2025-07-09

- 湖北初學(xué)FPGA開發(fā)板代碼 2025-07-09

- 遼寧核心板FPGA開發(fā)板編程 2025-07-09

- 上海開發(fā)FPGA開發(fā)板工業(yè)模板 2025-07-09

- 重慶安路開發(fā)板FPGA開發(fā)板工程師 2025-07-09

- 定制MEMS微納米加工服務(wù) 2025-07-10

- 青島塑料制品生產(chǎn)RFID讀寫器 2025-07-10

- 北京陶瓷基板蝕刻機價錢 2025-07-10

- 合肥圓形推拉自鎖連接器常見問題 2025-07-10

- INFIENON/英飛凌IPP139N08N3G代理商價格推薦 2025-07-10

- 新疆MEMS微納米加工電話 2025-07-10

- 廣州BZT52C27二極管代工 2025-07-10

- 內(nèi)蒙古伺服電機生產(chǎn)廠商 2025-07-10

- 防爆工業(yè)服務(wù)器大概價格多少 2025-07-10

- 高科技微流控芯片市場 2025-07-10